Hello guys , i have recently worked on vedic multipliers and have referred few papers too to implement it. I want to make this project open to everyone so that you can build your own Vedic multipliers and compare the results.Previously i have written about 2x2 bit Vedic multipliers which you can refer back again. We will start by designing a 2x2 multipliers and will develop a 16x16 multipliers. Once we are done with this we will proceed to build a MAC unit. A complete module which has 16x16 multiplier/MAC/ADD-SUB will be our end design

2X2 multiplier:

Design:

Figure illustrates the steps to to multiply two 2 bit numbers (design detail). Converting the above figure to a hardware equivalent we have 3 and gates which will act as 2 bit multipliers and two half adders to add the products to get the final product. Here is the hardware detail of the multiplier

Where "a" and "b" are two numbers to be multiplied and "q" is the product. With this design we are now ready to code this in verilog easily using and gates and HA(half adders). To make the design more modular we try to write code for HA first and then instantiate it to have the final product.

Code:

4X4 multiplier:

Design:

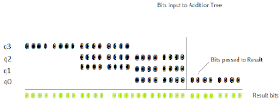

Using 4 such 2x2 multipliers and 3 adders we can built 4x4 bit multipliers as shown in the design. Proper instantiating of the 2x2 multipliers and adders. We have to first write code for 4bit and 6 bit adders. Its your choice to choose your adders. If in case you want to have better performance you can replace these normal adders with CSA or compressors. For a simpler design we have used the "+" operator which is supported by the XST synthesis tool which by default selects a low hardware adder. This architecture follows wallace tree which reduces the addition levels from 3 to just 2 stages as shown. Arrangement of the adders and the addition is explained from the figure shown below:

Code:

similar to the previous design of 4x4 multiplier , we need 4 such 4x4 multipliers to develop 8x8 multipliers. Here we need to first design 8bit and 12 bit adders and by proper instantiating of the module and connections as shown in the figure we have designed a 8x8 bit multiplier. At this point of time its necessary for you to even verify the RTL code and check if the hardware is as per your design. PlanAhead tool by xilinx gives better view of the hardware design with design elaborate option(will explain this in my next posts). Refer the addition tree diagram to know the process for 8x8 multiplier:

16x16 multiplier:

Design:

Here is the test bench for 16x16 vedic multipliers :

Simulation results:

RTL:

MAC design:

TO being with MAC design we have to first design a accumulator which adds two number . One of which is the output of the previous stage and the other is the output from the multiplier module. Figure below shows the implementation design for mac.

It can be seen from the block diagram that the accumulator module has one input( we have designed this module be be synchronous so we have used Clock as second input). Few more control signals are required to clear(clr) the ACC unit and enable signal(en) to initiate the process of accumulation. We replace the MUL unit shown in the diagram above with out 16x16 multiplier module. Here is the code for MAC unit

code:

Simulation results :

This module cane be further devloped to convert the top module into ALU by designing your own adder/substractor and making this as the top module. please let me know if there is anything you did not understand. We are happy to help. Thank you.

Note: Replace the modules with name "add_N_bit" with a N bit adder. You can use your own adder in place of this module like csa/cla etc. If speed is not of major concern for your design use the "+" operator to create the adder modules.

RTL:

Referece Papers:

Paper 1

Paper 2

contact: verilogblog@gmail.com

Simulation results:

MAC design:

TO being with MAC design we have to first design a accumulator which adds two number . One of which is the output of the previous stage and the other is the output from the multiplier module. Figure below shows the implementation design for mac.

It can be seen from the block diagram that the accumulator module has one input( we have designed this module be be synchronous so we have used Clock as second input). Few more control signals are required to clear(clr) the ACC unit and enable signal(en) to initiate the process of accumulation. We replace the MUL unit shown in the diagram above with out 16x16 multiplier module. Here is the code for MAC unit

code:

Simulation results :

This module cane be further devloped to convert the top module into ALU by designing your own adder/substractor and making this as the top module. please let me know if there is anything you did not understand. We are happy to help. Thank you.

Note: Replace the modules with name "add_N_bit" with a N bit adder. You can use your own adder in place of this module like csa/cla etc. If speed is not of major concern for your design use the "+" operator to create the adder modules.

RTL:

Referece Papers:

Paper 1

Paper 2

contact: verilogblog@gmail.com

Thanks a lot i was looking for this project. Good blog.

ReplyDeletethanks a lot ..:P

ReplyDeletecan i use this for m.tech project

ReplyDeleteYea you can use this for mtech project , provided you implement it on a fpga and compare with other multipliers with this one (delay,area,power)

Deletehiii

Deletehi ur code for 16 bit has errors can u please help me

Deletecan you please provide me a base paper for this one

ReplyDeleteto mail harishkumar.ece011@gmail.com

I will attach the PDF file to the post soon

Deletethank you sir

ReplyDeleteReference papers are attached, you can access it now, have a great day

Deletethank you very much sir for responding!!!!!!!!!!!

ReplyDeleteverilog coding is not displayed sir can you do the needful sir for Design and implementation of 16 Bit Vedic Arithmetic Unit

ReplyDeleteTry different browsers

Deletethanks ya pls mailing with them

ReplyDeleteYou can copy the code directly from the blog as it is text format. Thank you :)

Deletemy name is vighnesha i want 4x4 vedic multiplier entire code can you send me by email my email account is

ReplyDelete'karanth 973@gmail.com"

Code is already on the blog, You can use it

Deletei have tried this above multiplier (2x2) using reversible gate but in simulation output i find some of the bits in o/p shifted by 11..............

DeleteCode is already on the blog, You can use it

ReplyDeleteSIR I AM DOING MY PROJECT ON 8*8 VEDIC MULTIPLIER WITH BARREL SHIFT FOR FAST COMPUTATION.....

ReplyDeleteSIR PLEASE EXPLAIN THE ABOVE PROGRAM ELABORATELY AND HOW THE CARRY IS CORRECTLY USED IN FINAL ANSWER I CAN'T UNDERSTAND SIR.... PLEASE KINDLY HELP US AND GUIDE US....

THANK YOU SIR!!!!!!

Hello, please forward related papers to sgatesrobo@gmail.com. Will get back to you :) thank you

DeleteMY EMAIL ID:muthukumar1403@gmail.com... sir please kindly guide us

ReplyDeletehello sir,

ReplyDeletecan you send me the code for high speed vedic multiplier using reversible logic gate , please help me sir am doing this project and i have less time so please help me sir

We dont have the code for reversible logic as of now. If you have the design details of the multipliers please forward it to sgatesrobo@gmail.com. We will try to get back to you

DeletePLS SEND ME A FULL PROGRAM OF VEDIC MULTIPLIER SIR sivaji.kathi@gmail.com

ReplyDeleteYou can copy the code directly from the site.,

Deletewhere do i get those adders codes for vedic multiplier

ReplyDeleteCopy it from the blog, its in text format

Deletesir I am not getting this adder design can you send the specific link of same

Deletethis is charantej---conveying my congrats to represent the logic in diagramatic form for 4x4 vedic multiplier

ReplyDeletei am charan tej-----95244355 is my number pursuing mtech vlsi in vit university.

ur 4 by 4 multiplier is

///////////////////////////

module mul4by4(a,b,c);

input [3:0]a;

input [3:0]b;

output [7:0]c;

wire [3:0]q0;

wire [3:0]q1;

wire [3:0]q2;

wire [3:0]q3;

wire [7:0]c;

wire [3:0]temp1;

wire [5:0]temp2;

wire [5:0]temp3;

wire [5:0]temp4;

wire [3:0]q4;

wire [5:0]q5;wire [4:0]sp11,sp;

wire [5:0]q6;wire cary,cary1,cary2,cary21;wire [2:0]s;

// using 4 2x2 multipliers

vedic2by2 z1(a[1:0],b[1:0],q0[3:0]);

vedic2by2 z2(a[3:2],b[1:0],q1[3:0]);

vedic2by2 z3(a[1:0],b[3:2],q2[3:0]);

vedic2by2 z4(a[3:2],b[3:2],q3[3:0]);

// stage 1 adders

//assign temp1 ={2'b00,q0[3],q0[2]};

fa u0 (q1[0],q0[2],1'b0,q4[0],s[0]);

fa u1 (q1[1],q0[3],s[0],q4[1],s[1]);

fa u2 (q1[2],1'b0,s[1],q4[2],s[2]);

fa u3 (q1[3],1'b0,s[2],q4[3],cary);

//cary_seladd z5(q1[3:0],temp1,q4[3:0],cary1);

//add_4bit z5(q1[3:0],temp1,q4[3:0]);

assign temp2 ={2'b00,q2[3],q2[2],q2[1],q2[0]};

assign temp3 ={q3[3],q3[2],q3[1],q3[0],2'b00};

fa ur0 (temp2[0],temp3[0],1'b0,q5[0],sp[0]);

fa ur1 (temp2[1],temp3[1],sp[0],q5[1],sp[1]);

fa ur2 (temp2[2],temp3[2],sp[1],q5[2],sp[2]);

fa ur3 (temp2[3],temp3[3],sp[2],q5[3],sp[3]);

fa ur4 (temp2[4],temp3[4],sp[3],q5[4],sp[4]);

fa ur5 (temp2[5],temp3[5],sp[4],q5[5],cary1);

//cary_seladd z6(temp2,temp3,1'b0,q5,cary21);

//add_6bit z6(temp2,temp3,q5);

assign temp4={2'b00,q4[3],q4[2],q3[1],q3[0]};

// stage 2 adder

fa u1r0 (temp4[0],q5[0],1'b0,q6[0],sp11[0]);

fa u1r1 (temp4[1],q5[1],sp11[0],q6[1],sp11[1]);

fa u1r2 (temp4[2],q5[2],sp11[1],q6[2],sp11[2]);

fa u1r3 (temp4[3],q5[3],sp11[2],q6[3],sp11[3]);

fa u1r4 (temp4[4],q5[4],sp11[3],q6[4],sp11[4]);

fa u1r5 (temp4[5],q5[5],sp11[4],q6[5],cary21);

//cary_seladd z7(temp4,q5,1'b0,q6,cary21);//(a,b,cin,sum,co);

//add_6bit z7(temp4,q5,q6);

// fnal output assignment

assign c={q6[5],q6[4],q6[3],q6[2],q6[1],q6[0],q0[1],q0[0]};

endmodule

module fa( a1 ,b1 ,c1 ,sum1,carry1);

output sum1 ;

output carry1 ;

input a1 ;

input b1 ;

input c1 ;

assign sum1= a1 ^ b1 ^ c1;

assign carry1 = (a1&b1) | (b1&c1) | (c1&a1);

endmodule

We have verified the code with RTL. Any improvement is welcome.

Deleteits working properly without any error but some multiplication answers are not correct....

Deletefor example 13 multiply by 7 it showing 99

Deletesir when i am tried this code it show the error in that Vedic 2by2??

Deletewhat should i do

Hi..sir I want code for high

Deletespeed 16bit vedic multiplier..sir

This comment has been removed by a blog administrator.

ReplyDeleteSir ,i need your help for M.tech,project topic is 8 vedic multiplier and we need to optimize the power of 8 bit vedic Multiplier ,plz help me,My email id is rsgupta52@gmail.com.

ReplyDeleteSir, i need verilog code for 8 bit vedic multiplier to optimize the power ,plz help me sir,my email. id is rsgupta52@gmail.com

ReplyDeleteHello, If you are looking for power optimization then either you have to go for a low power architecture. In digital design using HDL the smallest comments are gates/mux etc which are of predefined area and delay. You can apply power reduction techniques in the transistor level design. So i suggest you to look for low power architecture and then go for design. Use cadence encounter tool for power analysis

Deletecan you pls post the code for accumulator?

ReplyDeletesir i need program for 8bit array multiplier... i completed my project.. please kindly post the program

ReplyDeleteHello, thanks for the post. However, this algorithm is for unsigned multiplication. What about signed number?

ReplyDeleteIs there any good way (low area/power/latency) to implement a signed version?

just declare the input and outputs as signed numbers, In simulation change the radix to signed decimal, You will get the results

Deletehye sir. sorry for asking this. i had tried declare input and output as signed number. how ever the result is wrong. could u please confirm it for me sir

Deleteplease reply and email to me at parentscontrolfree@gmail.com

Deletehello, sir plz tell me the how Arithmatic unit work for addition ,subtraction,multiplication and multiply and accumutae for different selection line? i am not able to understand how 4:1 mux work for 4 i/p addition,subtraction,multiplication ,and mac.but we want one out at a time according to selection line ie.s0 s1 00 addition ,01 substraction,10 multiplication,11 mac. plz give me ur mail id sothat i send my block diagram of arithmatic unit

ReplyDeletei have sended my block diagram at email sgatesrobo@gmail.com.plz explain when the function for addition,substraction ,multiplication,accumalation will perform,because we need one operation at time.

ReplyDeletefirst you have to write the code for all modules i.e adder/sub/acc. Then write a mux module with 2 bit select line. Just send the o/p of the modules to the mux and the select line will control which o/p to be sent.

Deletes0: addition

s1:sub:

s3:mac

s4:no operatoin

sir,why s4 for no operation ?we need one operation for multiplication also? my question is how s0=1,s1=1 work for mac and s1=1,s0=0 work for multiplication when control unit produce these two combination o/p for 4:1 mux .

Deleteconnect sos1=11 for multiplier o/p. U have to only connect the o/p pf the multiplier to the 4th input of mux . Declare the multiplier o/p as wire of required size . It will work

Deletecan u update 6 bit, 12 bit, 8bit csa code

ReplyDeletesir can u send the gate level circuit for vedic multiplier and how to combine the vedic multiplier in adiabatic logic if u can please send to my mail id.........

ReplyDeletehi ..sir. i am doing project on 8*8 vedic multliplier. i want to do it on both verilog simlation and layout design(using magic tool). please suggest me sir which technique i have to use for efficient design... thanking you sir..

ReplyDeletemy mail id: azmeeranarayana415@gmail.com

thank u sir.i am doing project in this area. this blog is very helpful to me.

ReplyDeletei have a verilog program for vedic multiplier.can u provide me the power area for my design

ReplyDeletecan i have 16 bit code for vedic multiplier using nikhilam sutra

ReplyDeletesir can u provide me code for vedic square using duplex method

ReplyDeletesir can you send me code for 3x3 vedic multiplier.......I need to develop a 24 bit vedic multiplier

ReplyDeletepls..for my project

my mail id: suganyaamirtharaj@gmail.com

sir send verilog code for 32bit mac unit to sklprasad480@gmail.com

ReplyDeleteHello VSLI Verilog

ReplyDeleteIt is definitely a great explanation. Could you please explain why this technique works though ? i.e., why we multiple and shift the way we multiply and shift?

Thanks

hello sir, my project is base on vedic multiplier - design an adaptive filter using Least mean square algorithm using vedic multiplier. can you please send me code of this?

ReplyDeletehello sir,

ReplyDeletei am a mtech student doing my project on the 4 x 4 vedic multiplier

will u please provide me the vhdl code for this,,

i will be very thankul to you....

sir accumulator code?

ReplyDeletesir can you send me code for 3x3 vedic multiplier.......I need to develop a 24 bit vedic multiplier

ReplyDeletepls..for my project

my mail id: jeus0910@gmail.com

can you plz send that 24 bit Vedic multiplier code to my mail ID .... naveenbkumarreddy@gmail.com

DeleteSir please help for design of accumulator

ReplyDeleteplease send me the accumulator code to mkrishna555@gmail.com mail id

ReplyDeleteSir i need code for the reversible vedic multiplier can you send me please

ReplyDeleteakshathadakshu02@gmail.com

Hello can u please send me this project code in verilog..... Majority voter of data encoder for NOC

ReplyDeleteI don't know much about verilog, but why do you pass the lower bits of q0 to c, but not the lower bits of q2 to q5?

ReplyDeleteIs there some overhead I'm not aware of?

how to compare araea time parameters i mean which tool

ReplyDeletei want a 24bit vedic multiplier to be used for floating point multiplier how to build it

ReplyDeleteSir I need verilog code for vedic divider...

ReplyDeletesir can I get the code for nikhilam sutra of the vedic multipliers??

ReplyDeleteif the code for 4x4 is simulating it is showing a warning that the blocks are unconnected to the module...how can i resolve it?

ReplyDeletesir i need a code for 16 bit vedic multiplier. i want the code for xilinx software. can u plz gv me the code.

ReplyDeletei want the code in order to dump it in spartan 2/3 kit.

hello sir i need to implement higher order modified wallace multiplier .i want to implement l 4 bit and want to instantiate i tried it like this but i am getting undetermined state(16'hxxxxxxxx)in output please help me i am very thankful to u .by instantiation i designed 64 bit multiplier

ReplyDeletemodule wallacetree64(clk,rst,md,mr,product);

input clk,rst;

input [63:0]md,mr;

output reg [127:0]product;

wire [63:0]p,q,r,s;

wire [63:0]x,y,z;

wire c1,c2,c3;

wallacetree32 u1(clk,rst,md[31:0],mr[31:0],p[63:0]);

wallacetree32 u2(clk,rst,md[63:32],mr[31:0],q[63:0]);

wallacetree32 u3(clk,rst,md[31:0],mr[63:32],r[63:0]);

wallacetree32 u4(clk,rst,md[63:32],mr[63:32],s[63:0]);

add41 u5(q,r,x,c1);

add42 u6(x,p[63:32],y,c2);

add43 u7(s,y[63:32],z,c1,c3);

always@(posedge clk)

begin

if(rst)

product=128'b0;

else product = {z,y[31:0],p[31:0]};

end

endmodule

/*******************************************/

module wallacetree32(clk,rst,md,mr,product);

input clk,rst;

input [31:0]md,mr;

output reg [63:0]product;

wire [31:0]p,q,r,s;

wire [31:0]x,y,z;

wire c1,c2,c3;

wallacetree16 u1(clk,rst,md[15:0],mr[15:0],p[31:0]);

wallacetree16 u2(clk,rst,md[31:16],mr[15:0],q[31:0]);

wallacetree16 u3(clk,rst,md[15:0],mr[31:16],r[31:0]);

wallacetree16 u4(clk,rst,md[31:16],mr[31:16],s[31:0]);

add31 u5(q,r,x,c1);

add32 u6(x,p[31:16],y,c2);

add33 u7(s,y[31:16],z,c1,c3);

always@(posedge clk)

begin

if(rst)

product=64'b0;

else product = {z,y[15:0],p[15:0]};

end

endmodule

/*******************************************************************************************88888*/

module wallacetree16(clk,rst,md,mr,product);

input clk,rst;

input [15:0]md,mr;

output reg [31:0]product;

wire [15:0]p,q,r,s;

wire [15:0]x,y,z;

wire c1,c2,c3;

wallacetree8 u1(clk,rst,md[7:0],mr[7:0],p[15:0]);

wallacetree8 u2(clk,rst,md[15:8],mr[7:0],q[15:0]);

wallacetree8 u3(clk,rst,md[7:0],mr[15:8],r[15:0]);

wallacetree8 u4(clk,rst,md[15:8],mr[15:8],s[15:0]);

add21 u5(q,r,x,c1);

add22 u6(x,p[15:8],y,c2);

add23 u7(s,y[15:8],z,c1,c3);

always@(posedge clk)

begin

if(rst)

product=32'b0;

else product = {z,y[7:0],p[7:0]};

end

endmodule

/*********************************************************/

module wallacetree8(clk,rst,md,mr,product);

input clk,rst;

input [7:0]md,mr;

output reg [15:0]product;

wire [7:0]p,q,r,s;

wire [7:0]x,y,z;

wire c1,c2,c3;

wallacetree4 u1(clk,rst,md[3:0],mr[3:0],p[7:0]);

wallacetree4 u2(clk,rst,md[7:4],mr[3:0],q[7:0]);

wallacetree4 u3(clk,rst,md[3:0],mr[7:4],r[7:0]);

wallacetree4 u4(clk,rst,md[7:4],mr[7:4],s[7:0]);

add1 u5(q,r,x,c1);

add2 u6(x,p[7:4],y,c2);

add3 u7(s,y[7:4],z,c1,c3);

always@(posedge clk)

begin

if(rst)

product=16'b0;

else product = {z,y[3:0],p[3:0]};

end

endmodule

/*********************************************************************************/

module wallacetree4(clk,rst,md,mr,product);

input clk,rst;

input [3:0]md,mr;

output reg [7:0]product;

integer i,j;

reg p[3:0][3:0];

wire [15:0]s;

wire [15:0]c;

always@(md,mr)

begin

for(i=0;i<4;i=i+1)

for(j=0;j<4;j=j+1)

p[i][j]=mr[i] & md[j];

end

ha1 u1(p[1][0],p[0][1],s[0],c[0]);

fa1 u2(p[2][0],p[1][1],p[0][2],s[1],c[1]);

fa1 u3(p[3][0],p[2][1],p[1][2],s[2],c[2]);

ha1 u4(p[3][1],p[2][2],s[3],c[3]);

ha1 u5(s[1],c[0],s[4],c[4]);

fa1 u6(s[2],c[1],p[0][3],s[5],c[5]);

fa1 u7(s[3],c[2],p[1][3],s[6],c[6]);

fa1 u8(p[3][2],c[3],p[2][3],s[7],c[7]);

ha1 u9(s[5],c[4],s[8],c[8]);

ha1 u10(s[6],c[5],s[9],c[9]);

ha1 u11(s[7],c[6],s[10],c[10]);

ha1 u12(p[3][3],c[7],s[11],c[11]);

ha1 u13(s[9],c[8],s[12],c[12]);

fa1 u14(s[10],c[9],c[12],s[13],c[13]);

fa1 u15(s[11],c[10],c[13],s[14],c[14]);

ha1 u16(c[11],c[14],s[15],c[15]);

always@(posedge clk)

begin

if(rst)

product=8'b0;

else product = {s[15:12],s[8],s[4],s[0],p[0][0]};

end

endmodule

i can u help u can u send me ur code with all add block then i will be sending u the modified wallace multiplier

DeleteThis comment has been removed by the author.

Deletecan you please send the code for add21 add22 and23

Deletewhat is the meaning of this statement in 4bit vedic multiplier

ReplyDelete"assign temp2 ={2'b0,q2[3:0]};"

Sir, please tell me how to design the adders used in the vedic algorithm module:the 4,6,8,12,16,24 bit adders. Please notify me with the adder modules.And what is the need of using the accumulator for 16x16 multiplication.

ReplyDeleteLooking forward for your reply sir.

Sir, also tell me how the addition tree accomplishes the vedic algorithm. Is it performing the shifting operation as in like a barrel shifter or something else. How does this addition tree does the vedic algorithm and yes please give the adder modules for 4 to 24 bit adder modules used in each of those coding's.

ReplyDeleteDear sir,

ReplyDeleteCan u send me the VLSI coding for 2x2 & 4x4 multiplier..

I'm in urgent need of it. Kindly send it as earilier as possible to info.sriram95@gmail.com

Thanks in advance. I look forward to hear from you soon.

sir, can u send me the accumulator stage verilog code of 16 bit mac to vpkvishnu3@gmail.com

ReplyDeleteThis comment has been removed by the author.

ReplyDeletesir please help me to code vedic divider

ReplyDeletecan u provide the code for 24*24 bit vedic multiplier using carry ripple adder..?

ReplyDeletesir may you provide vhdl code for vedic multiplier?

ReplyDeletei was implemented it for 32 bit fixed point number using vedic multiplier

Delete...

sir,I need the code of 8-bit vedic multiplier using barrel shifter by using nikhilam sutra.please help me.

ReplyDeletesir i need a code for "DESIGN AND IMPLEMENTATION OF 32-BIT VEDIC MULTIPLIER ON FPGA". PLEASE HELP ME

ReplyDeletehi we are final year btech students for our project we need 32 bit vedic multiplier please send the code if possible thank you

DeleteCan you post the code for add8 bits and add 12 bits code?

ReplyDeletehello sir;i run the code of 8*8 bit as you mentioned but it is showing error in the first line..can you please help me out

ReplyDeletewhat is the code for add_4_bit please help me out guys

ReplyDeleteHai. i am doing project on vedic maths for sram memory using verilog code. please send the code.

ReplyDeletei want code for accumulator

ReplyDeleteHow much delay did u got by this code for 2,4 & 8 bit in Spartan 3??

ReplyDeleteCan anyone tell me plzz....

Send vhdl code for 32 Vedic multiplier

ReplyDeleteHai sir, am monisha. Am doing 64 bit mac unit using vedic multiplier and reversible logic gates. Can u send me the code sir.

ReplyDeleteThis comment has been removed by the author.

ReplyDeleteThanks for sharing such an informative blog. This blog provides information about design-and-implementation-of-16-bit.This information will be useful to many professionals who want to know about Verilog.

ReplyDeleteFor more information visit: VERILOG Training in Lucknow

This comment has been removed by the author.

ReplyDeleteHi, I am M.Tech. student. As a part of my final project, I had implemented 32bit adder using both reversible logic gates and basic gates. According to the papers that I referred which was for a 8bit adder, the power dissipation and delay is comparatively less in reversible logic. But when I wrote the code for the same design, I observed that the power dissipation and the delay is more for the reversible gates. Could you please check the code and let me know the reason for this.

ReplyDeletehi sir i am doing my final year project on mac unit i need help cadence software i'm using

ReplyDeleteplease explain in detail about your problems .

Deletehallo sir! i've studied vedic 16x16, and i found that clock is used on schematic RLT, but power can not find it on 16x16 vedic code?

ReplyDeleteis there something wrong with the code?

and also I have studied the MAC codenya and there need code accumulator to compile it. Can I get all the codes sir? send me the code to niarboy03@gmail.com

thankyou!

This comment has been removed by the author.

ReplyDeletehallo sir! i've studied vedic 16x16, and i found that clock is used on schematic RLT, but i can not find it on 16x16 vedic code?

ReplyDeleteis there something wrong with the code?

or can you explaint about how can i placed clock on the code?

and also I have studied the MAC codenya and there need code accumulator to compile it. Can I get all the codes sir? send me the code to niarboy03@gmail.com

thankyou!

i need code of compressor adder, can you send me it on mukeshbth74@gmail.com

ReplyDeletehttp://verilog-code.blogspot.com/2018/08/books-to-buy-for-beginners-verilogvhdl.html

DeletePLS SEND VERILOG CODE FOR VEDIC MULTIPLIER USING YAVADANUM FORMULA

ReplyDeleteMAIL ID dorathyabisha@gmail.com

Deleteplz send bec using csla code

ReplyDeletemail id :dorathyabisha@gmail.com

Hello all,

ReplyDeleteCould someone explain the test bench code to me. How do the initial values work? I would like to be able to use the bits. Also, in the simulation picture it shows the values as hex. How can I change the values from bin to hex?

Cheers

hello all,

ReplyDeletethis site is waste f king bad the code up there is wrong lots of error

sir your programe explain method nice. i want to 32 bit vedic multiplier coding please send to me sir my mail id:viki7224@gmail.com

ReplyDeletehi we are final year students of btech for our project we need 32 bit vedic multiplier please send the code if possible it will help to our project thank you

Deletehello sir, can you provided matrix multiplication by using vedic multiplier

ReplyDelete???

email to me : irsyabab1996@yahoo.com

Do you see area/power savings with this architecture?

ReplyDeleteThis comment has been removed by the author.

ReplyDeletevedic_16x16 q1(a,b,clk,temp1); why clk is given as input because while designing vedic_16x16 u have mentioned only 2 inputs. So this will work

ReplyDeletePls kindly send the code for vedic multiplier using vedic signed multiplier using nikhilam algorithm

ReplyDeletepls kindly send the code for midpoint calculation for sqaured numbers in a sequence

ReplyDeleteSorry can you make 4x4=16 binary with vedic arithmetic unit project version?

ReplyDeletecan anyone make 4,6,8,12,16,24 address code

ReplyDeleteI can't find add_4_bit, add_6_bit, add_8_bit, add_12_bit, add_16_bit, add_24_bit code

plisss help me

email : line.up0108@gmail.com

I mean adder not addess

Deletesir while executing 2x2 multiplier it asks half adder sir please provide codes for that please

ReplyDeleteHello,

ReplyDeleteI want a help with the code of 8X8 vedic multiplier using carry select multiplier.

This comment has been removed by the author.

ReplyDelete