Abstraction is VLSI could be defined as the amount the information an entity is hiding within it. Consider a simple analogy of the universe. We can say that universe is huge(more hidden information) , It has planets and one of which is our earth (some details are revealed ), Earth is the 5th largest planet( more details )..... I hope you get the logic. The more detailed it is , the less information it is hiding and hence we may say that it is at the low level of abstraction. The more information it hides , higher is the abstraction level. Let us just get to VLSI now from planets :-) Consider you computer for example(system) , its at a higher level of abstraction, at the next level we have boards(mother board,cd drive,disks,etc) , next we have chip level( cpu etc), inside those chips (Now we are talking about VLSI abstraction) we have four levels of abstraction namely:

- Register level

- Gate level(logic gates, mux, decoder etc)

- circuit level (transistor)

- layout level (geometry )

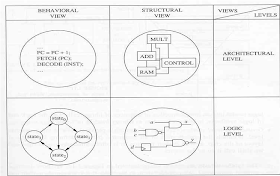

The figure explains the abstraction level in the deceasing order :

Designs can be expressed / viewed in one of three possible domains

- Behavioral Domain (Behavioral View- using boolean expressions )

- Structural/Component Domain (Structural View-connection of modules).

- Physical Domain (Physical View-layout).

A design modeled in a given domain can be represented at several levels of abstraction (Details). A circuit can be represented in three level as shown in the figure below

.....................................................................................

At architecture level its done using the available resources. Like "+" operator , predefined functions like "fetch" , "decode" etc....

......................................................................................

This is done using logical gates as shown or logical functions.

......................................................................................

Here each device appears like a geometric device and only the size, dimensions does matter here.

........................................................................................

A designer can view in either behavior level or structural level of physical level. Lets say we have a half adder design wherein we need a "and" gate and a "xor" gate. We first design these gates using behavioral description. once the gates are defined HA can be designed by instantiating the gates to give out sum and carry output for the adder. At the physical level each gate is described with its exact dimensions (layout) with its connection with other gates.

Figure below shows the abstractions ans corresponding views

Now let us try and make a simpler study about the different level of abstraction and the design views. Figure below will help you understand it better

System level:

- Behavioral : Its s written specification about the end product with focus on only the end functions ,power consumption, area

- Structural: Modules required for design is identified

- Physical: Physical partitioning, board size is defined

Chip level:

- Behavioral : behavior is explained using graphical charts and sometimes algorithms

- Structural: Chips in the design and their connection is shown

- Physical: size of pcb, etc, clusters(strongly connected components )

Register level:

- Behavioral : Data flow from the i/p port to the o/p port using registers and combinational blocks

- Structural: Components like ALU,MUX etc and their connection is shown

- Physical: Floor planning , standard cell

Gate level:

- Behavioral : Equation are used to define a function

- Physical: Module and cell plan

- Structural: Components are gates like and ,or , nand etc and their connection is show

Transistor level:

- Behavioral : Tx element equation

- Structural: components are transistor , resistors , capacitors etc

- Physical: Mask geometry

Daniel Gajski and Robert Kuhn developed a model called the "Y" model in 1983 which was refined by Donald Thomas it in 1985. Along the tree axis of this model are the 3 abstraction level with the design view in each level as shown in the figure below.

A designer can start with one perspective and may later switch to other in the chart. There is no hard rule to stick to one view on the "Y" model.

Points to remember :

- Behavior: This domain describes the temporal and functional behavior of a system.

- Structure: A system is assembled from subsystems. Here the different subsystems and their interconnection to each other is contemplated for each level of abstraction.

- Geometry: Important in this domain are the geometric properties of the system and its subsystems. So there is information about the size, the shape and the physical placement. Here are the restrictions about what can be implemented e. g. in respect of the length of connections.

- Architectural:A system’s requirements and its basic concepts for meeting the requirements are specified here.

- Algorithmic:The “how” aspect of a solution is refined. Functional descriptions about how the different subsystems interact, etc. are included.

- Functional block or register-transfer: Detailed descriptions of what is going on, from what register over which line to where a data is transferred, is the contents of this level.

- Logic: The single logic cell is in the focus here, but not limited to AND, OR gates, also Flip-Flops and the interconnections are specified.

- Circuit: This is the actual hardware level. The transistor with its electric characteristics is used to describe the system. Information from this level printed on silicon results in the chip.

THE ABSTRACTION IS VERY USEFUL SIR PLEASE CONTINUE THIS EDUCATION SERVICE

ReplyDeletethank you

DeleteReally its helpful .

ReplyDeleteReally, it is a useful information.

ReplyDeleteWhich software version should I use to excite the 32 bit vedic multiplier

ReplyDeleteuse any tool to simulate, xilinx it better option

DeleteThank alot sir for giving such a useful information.

ReplyDeleteThank You very much

ReplyDeleteWhich software & version should I use to design and analysis of CNFET Model based logic gates

ReplyDeleteThank you

ReplyDeleteReally Helpful. Great explanation. Thanks.

ReplyDelete