Link for the coupons : Here

Interpolation filter Design using Verilog Code.

interpolation factor = 2

coefficient number =10 ={1,0,0,0,0,0,0,0,0,0}

input sequence seq_in = {1,2,3,4,5,6,7,8,9....}

output sequence seq_out ={1,0,2,0,3,0,4,0,5,0,6....}

the below code helps us to get the interpolated sequence using interpolation factor 2

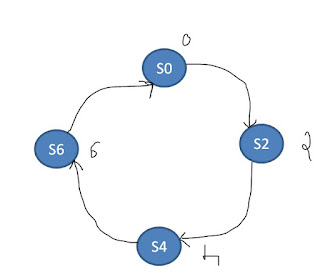

it uses the state machine and it is active low reset

every 10th clock the output is generated

//---------------function_multi.v------------------multiplication_function-------------------//

//---------------------used the function for multiplication---------------------------------//

module multiplication (input1 ,input2,output,clk,rst);

parameter WIDTH_IN=12 ;

parameter WIDTH_OUT=20 ;

input [WIDTH_IN-1:0]input1 ;

input [WIDTH_IN-1:0]input2 ;

input clk,rst ;

output [WIDTH_OUT-1:0]output ;

always@(posedge clk)

begin

if(!rst)

ouput<=0 ;

else

output<=input1*input2 ;

end

endmodule

//-------------------------------------------------------------------------------------------//

//-------------------------------------------------------------------------------------------//

//--------------------------------interpolTION-----------------------------------------------//

`include "function_multi.v" //multiplication function

//-----------------------------------------------------------------------------//

module interpolation(

seq_in ,//input sequence

seq_out ,//interpolated output sequence

rst ,//reset

clk //system clock

);

//-----------------------------------parameter------------------------------------------------//

parameter WIDTH_IN=12 ;//input width

parameter WIDTH_OUT=18 ;//output width

//----------------------------------COEFFICENTs-----------------------------------------------//

parameter signed H1= 1 ;//coefficents from h1 to h10

parameter signed H2= 0 ;

parameter signed H3= 0 ;

parameter signed H4= 0 ;

parameter signed H5= 0 ;

parameter signed H6= 0 ;

parameter signed H7= 0 ;

parameter signed H8= 0 ;

parameter signed H9= 0 ;

parameter signed H10=0 ;

//-----------------------------------------REGISTER-------------------------------------------//

reg signed [WIDTH_IN-1:0] q1, q2, q3, q4, q5, q6, q7, q8, q9,q10 ;//shift registers

reg signed [WIDTH_OUT-1:0]accum1 ;//accumulator for 1st clock of operation

reg signed [WIDTH_OUT-1:0]accum2 ;//accumulator for 2nd clock of operation

reg signed [WIDTH_OUT-1:0]accum3 ;//accumulator for 3rd clock of operation

reg signed [WIDTH_OUT-1:0]accum4 ;//accumulator for 4th clock of operation

reg signed [WIDTH_OUT-1:0]accum5 ;//accumulator for 5th clock of operation

reg signed [WIDTH_OUT-1:0]accum6 ;//accumulator for 6th clock of operation

reg signed [WIDTH_OUT-1:0]accum7 ;//accumulator for 7st clock of operation

reg signed [WIDTH_OUT-1:0]accum8 ;//accumulator for 8th clock of operation

reg signed [WIDTH_OUT-1:0]accum9 ;//accumulator for9th clock of operation

reg signed [WIDTH_OUT-1:0]accum10 ;//accumulator for 10th clock of operation

reg signed [WIDTH_IN-1:0]in1m1,in2m1 ;//input to 1st multiplier

reg [11:0]out ;//register for ring counter

reg [3:0]state=4'b0001 ;//state register

//---------------------------------------wire-------------------------------------------------//

wire [WIDTH_OUT-1:0]out_add ;//output from the multiplier

//----------------------------------------input------------------------------------------------//

input signed [WIDTH_IN-1:0]seq_in ;//input sequence

input clk,rst ;//system clock,reset

//-----------------------------------------output---------------------------------------------//

output reg signed [WIDTH_OUT-1:0]seq_out ;//output sequence

//------------------------------------------logic-------------------------------------------//

always@(posedge clk)begin

if(!rst)begin

accum1<=0 ;//reset=0,all register becomes zero

accum2<=0 ;

accum3<=0 ;

accum4<=0 ;

accum5<=0 ;

accum6<=0 ;

accum7<=0 ;

accum8<=0 ;

accum9<=0 ;

accum10<=0 ;

in1m1<=0 ;

in1m2<=0 ;

q1<=8'b00000000 ;

q2<=8'b00000000 ;

q3<=8'b00000000 ;

q4<=8'b00000000 ;

q5<=8'b00000000 ;

q6<=8'b00000000 ;

q7<=8'b00000000 ;

q8<=8'b00000000 ;

q9<=8'b00000000 ;

q10<=8'b00000000 ;

end

else

q1<=seq_in ;

q2<=q1 ;

q3<=q2 ;

q4<=q3 ;

q5<=q4 ;

q6<=q5 ;

q7<=q6 ;

q8<=q7 ;

q9<=q8 ;

q10<=q9 ;

end

//----------------------------------------------state machine---------------------------------//

always@(posedge clk)begin

case(state)

4'b0001:begin

in1m1<=q1 ;

in2m1<=H1 ;

accum1<=out_add ;

state<=4'b0010 ;

end

4'b0010:begin

in1m1<=q2 ;

in2m1<=H2 ;

accum2<=out_add ;

state<=4'b0011 ;

end

4'b0011:begin

in1m1<=q3 ;

in2m1<=H3 ;

accum3<=out_add ;

state<=4'b0100 ;

end

4'b0100:begin

in1m1<=q4 ;

in2m1<=H4 ;

accum4<=out_add ;

state<=4'b0101 ;

end

4'b0101:begin

in1m1<= q5 ;

in2m1<=H5 ;

accum5<=out_add ;

state<=4'b0110 ;

end

4'b0110:begin

in1m1<= q6 ;

in2m1<=H6 ;

accum6<=out_add ;

state<=4'b0111 ;

end

4'b0111:begin

in1m1<=q7 ;

in2m1<=H7 ;

accum7<=out_add ;

state<=4'b1000 ;

end

4'b1000:begin

in1m1<=q8 ;

in2m1<=H8 ;

accum8<=out_add ;

state<=4'b1001 ;

end

4'b1001:begin

in1m1<=q9 ;

in2m1<=H9 ;

accum9<=out_add ;

state<=4'b1010 ;

end

4'b1010:begin

in1m1<= q10 ;

in2m1<=H10 ;

accum10<=out_add ;

seq_out<=(accum1+accum2+accum3+accum4+accum5+accum6+accum7_accum8+accum9+accum10);//output calculated

state<=4'b0000 ;

end

//-------------------------------------------multipliers--------------------------------------//

multiplication m1(.clk(clk ),

.rst(rst),

.input1(in1m1),

.input2(in2m1),

.output(out_add)

);

endmodule

Please Note : Our course is now listed for Udemy training by Industry and leading companies use our courses :

Analog Design- Intuitive Approach

Rc Circuits Analysis With LT Spice

Basics of Mosfet - Simplified View

Please use these links or share with someone who might be interested.

Note : Author discounts are already applied to these links.